|

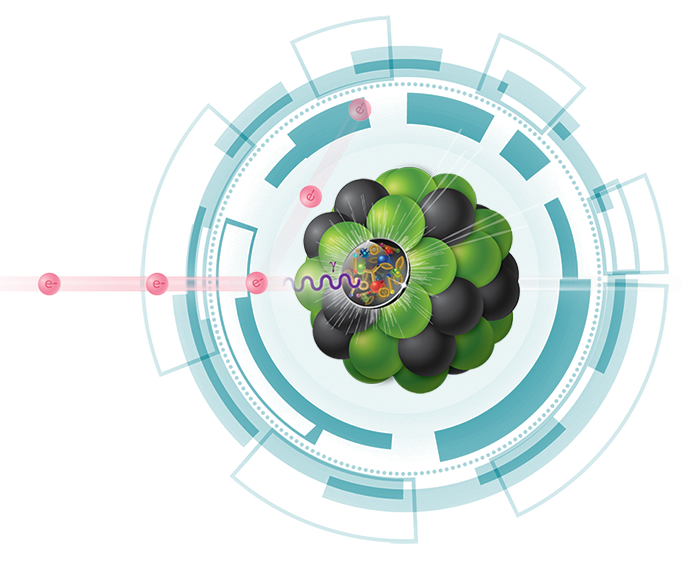

ECCE @ EIC Software

Reference for

ECCE @ EIC

simulation and reconstruction software on GitHub

|

|

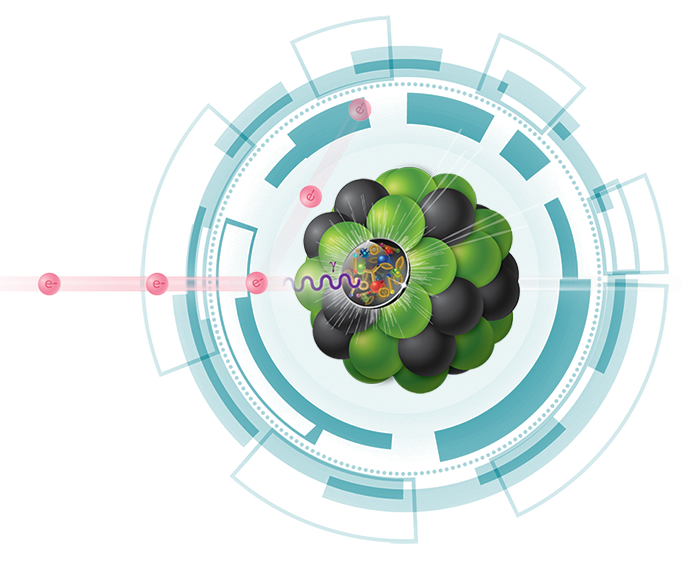

ECCE @ EIC Software

Reference for

ECCE @ EIC

simulation and reconstruction software on GitHub

|